|                                                            | DR. BABASAHEB AN                                                                                                                                                                                                                                                                                                                                                                                                               | IBEDKAR TECHNOLOGICAL UNIVERS                     | ITY, LONERE     |    |  |  |

|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-----------------|----|--|--|

| <b>Regular &amp; Supplementary Winter Examination-2023</b> |                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                   |                 |    |  |  |

|                                                            | Course: B. Tech. B                                                                                                                                                                                                                                                                                                                                                                                                             | sranch :Electronics Engineering                   | Semester : V    |    |  |  |

|                                                            | Subject Code & Name:                                                                                                                                                                                                                                                                                                                                                                                                           | (BTEXOE505A) Digital System Design                |                 |    |  |  |

|                                                            | Max Marks: 60                                                                                                                                                                                                                                                                                                                                                                                                                  | Date:10-01-24                                     | Duration: 3 Hr. |    |  |  |

|                                                            | <ol> <li>Instructions to the Students:         <ol> <li>All the questions are compulsory.</li> <li>The level of question/expected answer as per OBE or the Course Outcome (CO) on which the question is based is mentioned in () in front of the question.</li> <li>Use of non-programmable scientific calculators is allowed.</li> <li>Assume suitable data wherever necessary and mention it clearly.</li> </ol> </li> </ol> |                                                   |                 |    |  |  |

| Q. 1                                                       | Solve Any Two of the fol                                                                                                                                                                                                                                                                                                                                                                                                       | lowing.                                           |                 | 12 |  |  |

| A)                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                | ata objects with syntax in VHDL File, sig         | gnal, CO4       | 6  |  |  |

| B)                                                         | Variable, file.<br>Explain the various data types in VHDL.                                                                                                                                                                                                                                                                                                                                                                     |                                                   | <b>CO4</b>      | 6  |  |  |

| C)                                                         | Write different types of de                                                                                                                                                                                                                                                                                                                                                                                                    | elays used in VHDL.                               | CO4             | 6  |  |  |

| Q.2                                                        | Solve Any Two of the fol                                                                                                                                                                                                                                                                                                                                                                                                       | lowing.                                           |                 | 12 |  |  |

| A)                                                         | What is subprogram? Exp                                                                                                                                                                                                                                                                                                                                                                                                        | lain 'Function' and 'Procedure' with their syntax | к. <b>СО4</b>   | 6  |  |  |

| B)                                                         | What is the purpose of test bench in VHDL? Design Half Adder and write test bench code.                                                                                                                                                                                                                                                                                                                                        |                                                   | vrite CO1, CO4  | 6  |  |  |

| C)                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                | f component declaration and instantiation         | with CO1, CO4   | 6  |  |  |

| Q. 3                                                       | Solve Any Two of the fol                                                                                                                                                                                                                                                                                                                                                                                                       | lowing.                                           |                 | 12 |  |  |

| A)                                                         | Design half-subtractor and                                                                                                                                                                                                                                                                                                                                                                                                     | Write a VHDL code using behavioral modeling       | ng. CO1         | 6  |  |  |

| B)                                                         | Design 3:8 decoder and w                                                                                                                                                                                                                                                                                                                                                                                                       | rite VHDL code using structural modeling.         | CO2             | 6  |  |  |

| C)                                                         | Design a full-adder using                                                                                                                                                                                                                                                                                                                                                                                                      | two half-adders and write VHDL code for it.       | C01             | 6  |  |  |

| 04                                                         | Solve Any Two of the fol                                                                                                                                                                                                                                                                                                                                                                                                       | lowing                                            |                 | 12 |  |  |

## Q.4 Solve Any Two of the following.

- 12

- A) Define FSM. Also Differentiate between Mealy and Moore machines. CO3 6

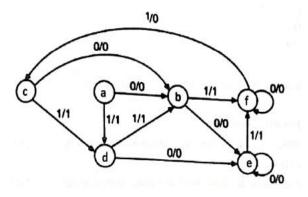

- **B**) Reduce the following state diagram and prepare a state table for reduced **CO3 6** state diagram.

| C)   | Draw the Melay state diagram for sequence detector 1001 and 0110.                          | CO3 | 6  |

|------|--------------------------------------------------------------------------------------------|-----|----|

| Q. 5 | Solve Any Two of the following.                                                            |     | 12 |

| A)   | Explain the following terms in details<br>i. Clock skew<br>ii. Dynamic Hazards<br>iii. PLD | CO3 | 6  |

| B)   | Explain Metastability and Synchronizers.                                                   |     | 6  |

| C)   | Briefly explain the architecture of a Complex Programmable Logic Device                    | CO4 | 6  |

|      | *** End ***                                                                                |     |    |